Introduction

FPGA pattern is non a simple flake quantum only mainly uses its model to pattern products in other industries. From the perspective of chip devices, FPGA itself constitutes a typical integrated circuit in a semi-custom circuit, which contains digital management modules, embedded units, output units, and input units. On this basis, information technology is necessary to focus on the comprehensive bit optimization design of FPGA fries, and add new chip functions by improving the electric current scrap blueprint, thereby realizing the simplification of the overall structure of the fleck and the improvement of operation. Therefore, when using it, you must understand its design principles in order to better improve its performance.

FPGA Design Tips

ane) Series to Parallel Conversion

Information technology is an important skill in FPGA blueprint, a mutual method for data stream processing, and a direct reflection of the idea of area and speed interchange. There are various implementation methods for series-parallel conversion. According to the data ordering and quantity requirements, the post-obit methods can be selected: registers for small blueprint, ROM for large data volumes, state machines for circuitous serial-parallel conversion, or direct utilize of functions module to implement.

2) Pipelining

Pipelining is a frequently used blueprint method in loftier-speed design. If the processing flow of a certain data is divided into several steps, and the entire data processing is "unmarried menstruation", that is, there is no feedback or iterative operation, and the output of the previous footstep is the input of the next step, the pipeline design method can be used to ameliorate the operating frequency of the organization.

- During pipeline design, the timing sequence should exist arranged reasonably, the division of each operation step should be reasonable, and the data menses betwixt each step should be carefully considered.

- If the pre-stage operation time is exactly equal to the post-phase operation time, the design is the nearly simple, and the pre-stage output direct to the post-stage input will do.

- If the functioning time of the previous stage is longer than the operation time of the latter stage, the latter stage will often be idle, and the data of the quondam stage can be properly buffered and then output to the input stop of the latter phase.

- If the operation time of the previous stage is less than the functioning time of the subsequent stage, the data flow must be distributed and preprocessed in parallel through the replication logic, or the data should be stored and post-processed in the previous stage, otherwise it volition cause the data overflow of the later stage. Therefore, how to residuum the processing time of each module should be given due consideration in the design.

3) ATA Interfaces

- If the beat of the input data is the same frequency every bit the processing clock of the system, the input data register can be sampled straight with the master clock of the system to complete the synchronization of the input information.

- If the input information and the processing clock of the organisation are asynchronous, use the processing clock to sample the input information twice (or multiple times) of the register to consummate the synchronization of the input information. The issue of double (or multiple) sampling is to suppress the propagation of metastability and is suitable for a small number of functional units that are insensitive to errors.

- In gild to avoid the wrong sampling level in the asynchronous clock domain, by and large utilize the RAM and FIFO storage methods to complete the data conversion of the asynchronous clock domain, and use the upper level in the input port.

4) Comparing of Effective Coding and If-And then-Else

In the combination process and the country process, If-And then-Else and instance statements may be used, the synthesized results are the same equally the combinational logic, just in that location will be differences. The case argument is implemented past a module, and the If-So-Else is used, decoder implementation with privileged encoding.

5) Latches and Registers

The latch is level-effective, and in the case of level-effective, the input is sent to the output. For case, the register is valid on the clock border and but outputs when the clock arrives. In improver to the lookup tabular array, there are registers in the logic unit, and so it is recommended that you use the registers that are valid along the border, and do not use the latches implemented by adding combinational logic.

half dozen) Clock Enable

The manner the VHDL program is coded will determine whether to utilize the clock enable signal, which makes timing constraints easier to control.

seven) Tri-states

The IEEE standard defines the Z value of the tri-state in the STD_LOGIC software package. That is, the simulation is a loftier-impedance state, and information technology is converted into a tri-state buffer during synthesis.

Only the I/0 cells of Altera devices accept tri-state buffers, which has the advantage of eliminating possible omnibus connections and solving internal logic placement issues. Because no tri-land buffer is required, device testing is reduced and costs are saved. The internal 3-state must be converted into combinational logic, and the complex output enable is easy to cause errors and low-efficiency logic, but there is a 3-country buffer in the I/O unit.

eight) Bidirectional Pin

When the pin is specified as the direction INOUT, the INOUT pin is used as input or tri-land output. In the plan, a bi-management is set to act equally a bidirectional INOUT bespeak. When the CE enable signal is equal to 1, the from core signal from the core is sent to the bi-directional pin, otherwise, it is tri-land. At this time, the bi-directional is used as a tri-land output, and there is also an input assigned, the betoken from the core is sent to the tri-state, the input is sent to the kernel.

ix) Memory Storage

Synthesis tools have unlike capabilities to identify diverse memories. In order to place the diverse memories, synthesis tools are very sensitive to specific decoding types, which are unremarkably specified in the synthesis tool file. The synthesis tool may accept some restrictions on the structure implementation, such every bit only synchronous writes, clock configuration restrictions, memory size restrictions, etc., an array data type must be specified to agree the memory value. The retentiveness includes unmarried port memory, single port dual clock memory, dual clock memory, ROM then on.

Programming Language

Verilog HDL, as an HDL language, models system behaviour is in a hierarchical manner. The more of import levels are arrangement level, algorithm level, register transfer level (RTL), logic level, gate level, excursion switch level.

Regarding the for loop, in actual piece of work, except for the use of the for loop statement when describing the simulation test stimulus (Testbench), the for loop is rarely used in RTL-level coding, because the for loop volition exist expanded past the synthesizer into the execution of all variable cases statement, each variable independently occupies register resource, which cannot effectively reuse hardware logic resources, resulting in huge waste. Generally, we often employ example statements instead.

In addition, there is a large difference betwixt if...else...and the instance in the nested description, which has priority. More often than not speaking, the first "if" has the highest priority, and the last "else" has the lowest priority. The instance argument is a parallel statement, it has no priority, and the establishment of a priority construction requires a lot of logic resources, so do not employ if...else... statement where instance can exist used.

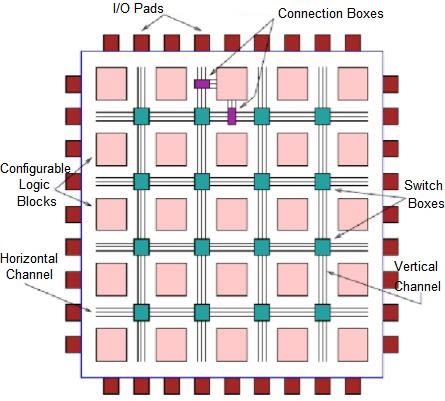

FPGA Basic Architecture

FPGA Pin Consignment Principles

In the evolution of the fleck, FPGA verification is an important part. How to effectively use the resource of the FPGA, pivot consignment is also an important issue that must exist considered. Generally, a better method is to automatically allocate the corresponding tools through some timing constraints during the synthesis process, but this method is oftentimes not desirable from the time period of inquiry and development, and the RTL verification and board design must be carried out synchronously. When the verification code comes out, the board to be verified must besides be designed, that is, the pin assignment must too be completed before the design code comes out. Therefore, the assignment of pins will depend more on people than tools. At this time, diverse factors demand to be considered.

In summary, the following aspects are mainly considered:

ane) The Indicate Flow of the Logic Carried by the FPGA.

The FPGA used in IC verification generally has a very large logic capacity and a large number of external pins. At this time, the difficulty of wiring during PCB pattern must be considered. If the pivot consignment is unreasonable, information technology may be a big number of crossed indicate lines in PCB design, which brings neat difficulties to the wiring or fifty-fifty fails to go through, or even if the wiring goes through, information technology may not encounter the timing requirements due to the excessive external delay. Therefore, earlier the pivot assignment, you should exist quite familiar with the working environment of the FPGA, and you should be very clear about where the signals come up from and where they are going. In this way, according to the principle of the shortest connexion, the respective signals are assigned to the closest connection to the external device in BANK.

two) Master the Resource allotment of BANK within the FPGA.

FPGAs are now divided into several areas internally, and the number of I/O pins available in each area varies. In the IC verification, FPGAs of the ALTERA and XILINX series are used. There are certain differences in the resource allotment of internal banks in the FPGAs of these two manufacturers. Only you tin refer to the relevant manuals in the pattern. The post-obit is an example of the allocation of Banking company inside the FPGA of the Stratix II series in ALTERA.

The allotment of BANKs inside the FPGA and the I/O standards are supported in each BANK. Co-ordinate to the distribution of the internal banks in the FPGA, the flow direction of the signals can be roughly fixed. The direction of the FPGA in the unmarried board, and at the same time, the related signals are distributed to the related banks co-ordinate to the principle of proximity. This method can consummate the distribution of general signals.

3) Master the I/O standards supported by each bank of the selected FPGA.

It can be seen that the I/O standards supported by each banking concern in the FPGA are non the aforementioned, and so the pins that support the same standard should be full-bodied in 1 bank when assigning pins because the same standard in the FPGA is required. A bank by and large does not back up two I/O standards at the same time, of course, there are exceptions, which requires consulting the working weather required past the relevant I/O standards.

4) Pay Attending to the Assignment of Pins for Special Signals.

The special signals here mainly refer to the clock signal and the reset indicate, or some signals that require loftier driving capability. The clock signal is generally required to be distributed to the global clock pin so that the fourth dimension delay obtained in this manner will be the smallest and the drive volition be the strongest. Because the reset signal requires practiced synchronization and strong driving ability, information technology is also sent from the global clock pin under normal circumstances. When allocating clocks, the allocation strategies vary greatly according to the number of clocks, and you need to pay attending. It is necessary to refer to the respective manual to see where clocks vest to. Generally, the clocks are differential. At this fourth dimension, if the clocks used are not, yous should pay attention to that the P terminal and the N terminal generally cannot be assigned to different clock signals at the aforementioned fourth dimension. Anyhow, if the paired clocks in the XILINX series of FPGAs are used at the same time, they cannot reach the same area at the aforementioned time, because at that place is merely one clock line that reaches the same area.

Therefore, it is best non to use pairs of P and S at the same time when there are few clocks, but just cull P or N so that there will exist no disharmonize.

5) The Consideration of Point Integrity.

Since charabanc consignment often occurs in the assignment, and a big number of buses may ofttimes be flipped at the same fourth dimension, this will bring a series of signal integrity problems separately.

0 Response to "How Wide Of A Register Can You Have In Fpga"

Post a Comment